# JireStar/JireStar ACPI

## 64-Bit CPU Single Chip Notebook Solution

**Preliminary Data Book**

Revision: 1.0 912-2000-015 February 28, 1997

#### Copyright

Copyright © 1997, OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of OPTi Inc., 888 Tasman Drive, Milpitas, CA 95035.

#### **Disclaimer**

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### **Trademarks**

OPTi and OPTi Inc. are registered trademarks of OPTi Inc. All other trademarks and copyrights are the property of their respective holders.

#### **OPTi Inc.**

888 Tasman Drive Milpitas, CA 95035 Tel: (408) 486-8000

Fax: (408) 486-8001 WWW: http://www.opti.com/

888 Tasman Drive Milpitas, CA 95035 (408) 486-8000 Fax: (408) 486-8001

### **Revision Document**

Product Name: FireStar / FireStar ACPI (82C700) Single-Chip Notebook Solution

Document Title: Preliminary Data Book (#912-2000-015) Revision 1.0

Date: February 28, 1997

### Scope

This document provides the revisions that have been incorporated in Revision 1.0 of the 82C700 Preliminary Data Book, #912-2000-015 since Revision 0.2 dated May 8, 1996.

The data book includes details regarding FireStar ACPI (hence the name change of the data book) and denotes, where appropriate, if the discussion is applicable only to FireStar ACPI.

#### **Revision History (0.2 to 1.0)**

#### Section 1.0 Features

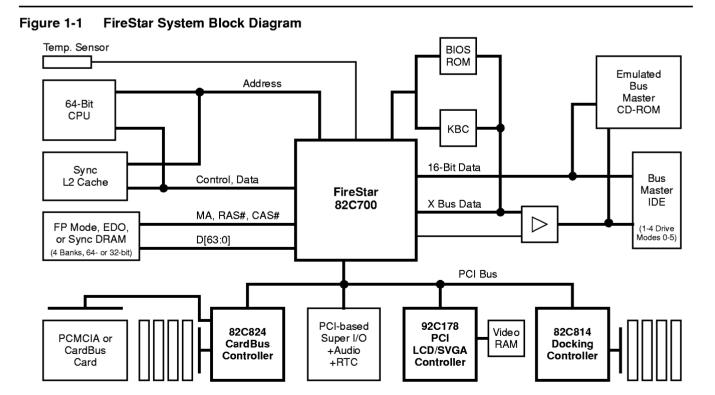

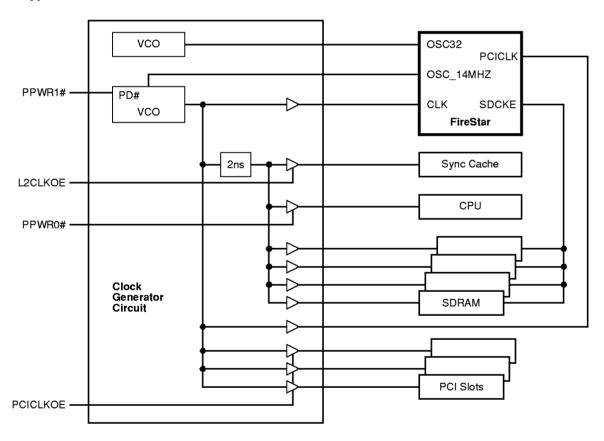

- Figure 1-1 FireStar System Block Diagram

- Designated PCI bus

- Modified address line

- Changed name of CPU (was designated as 64-Bit 586 CPU - FireStar supports both 586- and 686-class)

- · Removed Unified Memory Interface (totally)

- · Added ACPI Implementation bullet

#### Section 2.0 Overview

· No changes

#### Section 3.0 Signal Definitions

#### 3.1 Terminology/Nomenclature Conventions

· No changes

#### 3.2 Signal Descriptions

Summary the major changes made to the pin function assignments:

- Removed Boundary Scan Signal functions (all except TMS)

- · Removed UMA interface functions

- Changed three of the VCC\_CPU power pins to CPU\_CORE (AB19, H22, K5) in preparation for future 2.5V CPU interface

Summary of the general format changes made:

- Expanded greatly on detailing of individual signal descriptions

- Designated in "Pin No." column of description tables which pins are used as strap option selection pins

- Clearly specified which PIO pins could be programmed as outputs only (PIO0 through PIO5) in description tables

- Adjusted pin diagram (Figure 3-1), alphabetical pin crossreference list (Table 3-2) and the signal descriptions accordingly with the pin modifications listed in Table 1 (of this document

Table 1 (of this document) lists the actual pin modifications between data book 0.2 and 1.0 (alphabetically).

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

### **Revision Document**

#### Table 1 FireStar Pin Modifications

| Data Book Rev. 0.2<br>Signal Name | Pin No. | Data Book Rev. 1.0<br>Signal Name      |

|-----------------------------------|---------|----------------------------------------|

| BWE#+RAS4                         | P4      | BWE#                                   |

| CAS0#                             | B10     | CAS0#+SDDQM0#                          |

| CAS1#                             | C10     | CAS1#+SDDQM1#                          |

| CAS2#                             | D10     | CAS2#+SDDQM2#                          |

| CAS3#                             | A11     | CAS3#+SDDQM3#                          |

| CAS4#                             | B11     | CAS4#+SDDQM4#                          |

| CAS5#                             | C11     | CAS5#+SDDQM5#                          |

| CAS6#                             | D11     | CAS6#+SDDQM6#                          |

| CAS7#                             | A12     | CAS7#+SDDQM7#                          |

| CDOE#                             | P1      | CDOE#+PIO0                             |

| CMD#+PCICLK3                      | AB20    | CMD#+DIRTY+PCICLK3                     |

| DWE#                              | E10     | DWE#+SDWE#                             |

| EADS#                             | T4      | EADS#+WB/WT#                           |

| GNT3#+UMAGNT#                     | AC18    | GNT3#                                  |

| IRQSER+SOUT#                      | AE18    | IRQSER+SDCKE+SOUT#                     |

| 32KHZ                             | C7      | OSC32                                  |

| PWRGD+TRST#                       | H26     | PWRGD                                  |

| RAS0#                             | E12     | RAS0#+SDCS0#                           |

| RAS1#+PIO5                        | E13     | RAS1#+SDCS1#+PIO5                      |

| RAS2#+PIO4                        | B12     | RAS2#+SDCS2#+PIO4                      |

| RAS3#+MA12                        | C12     | RAS3#+SDCS3#+MA12                      |

| RSVD                              | E22     | RAS4#+MA12                             |

| REQ3#+UMAREQ#                     | AD18    | REQ3#                                  |

| тск                               | A8      | SDCAS#                                 |

| TMS                               | D7      | SDRAS#                                 |

| SEL#/ATB#+PIO14                   | AC20    | SEL#/ATB#+SDCKE+PIO14                  |

| TAG0                              | E9      | TAG0+CAS0#                             |

| TAG1+START#                       | D9      | TAG1+CAS1#+START#                      |

| TAG2+START#                       | C9      | TAG2+CAS2#+START#                      |

| TAG3+SBOFF#                       | В9      | TAG3+CAS3#+SBOFF#                      |

| TAG4                              | A9      | TAG4+CAS4#+SDCKE                       |

| TAG5                              | D8      | TAG5+CAS5#+DWE#                        |

| TAG6                              | C8      | TAG6+CAS6#+SDCAS#                      |

| TAG7                              | В8      | TAG7+CAS7#+SDRAS#                      |

| TDI                               | B7      | RSVD                                   |

| TDO                               | A7      | SDCKE (FS ACPI, RSVD in non-ACPI ver.) |

| RSVD                              | AB5     | TMS                                    |

| VCC_CPU                           | H22     | VCC_CORE                               |

| VCC_CPU                           | K5      | VCC_CORE                               |

| VCC_CPU                           | AB19    | VCC_CORE                               |

| W/R#                              | AA5     | W/R#+INV                               |

#### 3.3 Programmable I/O Pins

- · Added note in opening text:

- "Any signal that can potentially be programmed as a PIO pin will function as a PIO pin only if the corresponding CPU register is programmed to a non-zero value."

- Table 3-3 PIO Functions

- Misc. Outputs Group 3h

Added functions: FAN, PCTLL, ATCLK/2

- IDE Controller Outputs Group 4h

Added functions: DDACK0-0#, DDACK0-1#,

DDACK1-0#, DDACK1-1#

- ACPI Inputs Group 7h New group added to table

- Table 3-6 Register Programmable PIO Pins

- Added corresponding pin names in register titles for easier reading

#### 3.4 Strap Selected Options

- Table 3-7 Strap Options

- Added corresponding pin number to table

- Added BOFF# strap option

- Combined RTCAS and A20M# into one strap option, RTCAS:A20M#

- Added PCICLK0 strap option

- Added RSVD strap option (preparation for 2.5V CPU interface future revision)

- Table 3-8 Strap Option Readback Registers

- New table

#### **Section 4.0 Functional Description**

Major revisions to the functional description section include:

- Removed UMA Support (was Section 4.9)

- Added new section on ACPI Implementation (currently Section 4.16)

- Rearranged IDE Interface section for better flow and provided more details on emulated bus master mode

- Added SDRAM detection algorithm in DRAM Controller section

- Pulled all clock information into one section (System Clocks, Section 4.4)

#### Section 5.0 Register Descriptions

• Added the following notes to opening text:

- Notes: 1. Bits/registers that are new or have changed (between Data Book Rev 0.2 and Data Book Rev 1.0), are underlined and denoted with a change bar in the margin.

- 2. All bits/registers are read/write and their default value is 0 unless otherwise specified.

- 3. All reserved bits/registers MUST be written to 0 unless otherwise specified.

In this portion of the revision document, the tables that correspond to the register tables in the data book will specify either:

- a. No change,

- reference only the bits/registers that are new or changed, and if any

- default changes

#### **SYSCFG Register Space** 5.1

· No changes to opening text.

#### Table 5-5 SYSCFG 00h-FFh

| Loc. | Register Name                                               | Revision                             |

|------|-------------------------------------------------------------|--------------------------------------|

| 00h  | Byte Merge/Prefetch & Sony<br>Cache Module Control Register | No change                            |

| 01h  | DRAM Control Register 1                                     | No change                            |

| 02h  | Cache Control Register 1                                    | Bits [7,6]                           |

| 03h  | Cache Control Register 2                                    | No change                            |

| 04h  | Shadow RAM Control Register 1                               | Added text to foot-<br>notes 2 and 3 |

| 05h  | Shadow RAM Control Register 2                               | No change                            |

| 06h  | Shadow RAM Control Register 3                               | No change                            |

| 07h  | Tag Test Register                                           | No change                            |

| 08h  | CPU Cache Control Register                                  | Bits [4,2]                           |

| 09h  | System Memory Function Register                             | No change                            |

| 0Ah  | DRAM Hole A Address Decode<br>Register                      | No change                            |

| 0Bh  | DRAM Hole B Address Decode<br>Register                      | No change                            |

| 0Ch  | DRAM Hole Higher Address                                    | Bits [7,5,4]                         |

| 0Dh  | Clock Control Register                                      | Bits [7:4]                           |

| 0Eh  | PCI Master Burst Control Register 1                         | Bits [7:4]                           |

| 0Fh  | PCI Master Burst Control Register 2                         | Bits [7,5:3,1,0]                     |

| 10h  | Miscellaneous Control Register 1                            | No change                            |

| 11h  | Miscellaneous Control Register 2                            | Bits [4,3,1]                         |

| Loc.        | Register Name                          | Revision                                       |

|-------------|----------------------------------------|------------------------------------------------|

| 12h         | Refresh Control Register               | Bits [7,0]                                     |

| 13h         | Memory Decode Control Register         | No change                                      |

| 14h         | Memory Decode Control Register 2       | No change                                      |

| 15h         | PCI Cycle Control Register 1           | No change                                      |

| 16h         | Dirty/Tag RAM Control Register         | Bits [7,5], new foot-<br>note, default changed |

| 17h         | PCI Cycle Control Register 2           | Bit [5]                                        |

| 18h         | Interface Control Register             | Bit [6]                                        |

|             | FS ACPI                                | Bits [7,3,1]                                   |

| 19h         | Memory Decode Control Register 3       | Bits [3:0]                                     |

| 1Ah         | Memory Shadow Control Register 1       | No change                                      |

| 1Bh         | Memory Shadow Control Register 2       | No change                                      |

| 1Ch         | EDO DRAM Control Register              | No change                                      |

| 1Dh         | Miscellaneous Control Register 3       | Bits [6,2]                                     |

| 1Eh         | Control Register                       | Bits [6,4,2]                                   |

| 1Fh         | EDO Timing Control Register            | Bits [5,2,1]                                   |

| 20h         | DRAM Burst Control Register            | Bits [7,5]                                     |

| 21h         | PCI Concurrency Control Register       | Bit [0], default<br>changed                    |

| 22h         | Inquire Cycle Control Register         | Bits [7,5]                                     |

| 23h         | Pre-Snoop Control Register             | Bits [6,3:1]                                   |

| 24h         | Asymmetric DRAM Configuration Register | No change                                      |

| 25h         | GUI Memory Location Register           | Bits [7:3,2,0]                                 |

| 26h         | UMA Control Register 1                 | Bits [7,5,4,2:0]                               |

| 27h         | Miscellaneous Control Register 4       | Bits [6,5,3,2:0]                               |

| 28h         | SDRAM Control Register 1               | Bits [7:0]                                     |

| 29h         | SDRAM Control Register 2               | Bits [7:0]                                     |

| 2Ah         | PCI-to-DRAM Control Register 1         | Bits [7:0]                                     |

| 2Bh         | PCI-to-DRAM Control Register 2         | Bits [7:0]                                     |

| 2Ch         | CPU-to-DRAM Buffer Control<br>Register | Bits [6,5,3,1], new footnote                   |

| 2Dh         | Miscellaneous Control Register 5       | Added text to footnote                         |

| 2Eh         | UMA Control Register 2                 | Bits [7:4,1,0]                                 |

| 2Fh         | UMA Control Register 3                 | Bits [7:0], footnote                           |

| 30h-<br>37h | Reserved                               | No change                                      |

| 38h         | NMI Trap Enable Register 1             | No change                                      |

| 39h         | NMI Trap Enable Register 2             | No change                                      |

| 3Ah         | NMI Trap Enable Register 3             | No change                                      |

| 3Bh         | NMI Trap Enable Register 4             | No change                                      |

| 3Ch         | NMI Trap Enable Register 5             | No change                                      |

| 3Dh-<br>3Fh | Reserved                               | No change                                      |

## **Revision Document**

#### Table 5-5 SYSCFG 00h-FFh (cont.)

| Loc. | Register Name                                          | Revision                              |

|------|--------------------------------------------------------|---------------------------------------|

| 40h  | PMU Control Register 1                                 | Bit [7]                               |

| 41h  | DOZE_TIMER Register                                    | No change                             |

| 42h  | If AEh[7] = 0: Clock Source Register 1                 | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: Clock Source Register 1 A               | New bits available "If<br>AEh[7] = 1" |

| 43h  | PMU Control Register 2                                 | No change                             |

| 44h  | LCD_TIMER Register                                     | No change                             |

| 45h  | DSK_TIMER Register                                     | No change                             |

| 46h  | KBD_TIMER Register                                     | No change                             |

| 47h  | If AEh[7] = 0: GNR1_TIMER<br>Register                  | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: GNR5_TIMER Register                     | New bits available "If AEh[7] = 1"    |

| 48h  | If AEh[7] = 0: GNR1 Base<br>Address Register           | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: GNR5_Timer<br>Base Address Register     | New bits available "If AEh[7] = 1"    |

| 49h  | If AEh[7] = 0: GNR1 Control<br>Register                | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: GNR5_Timer Control Register             | New bits available "If AEh[7] = 1"    |

| 4Ah  | Chip Select 0 Base Address Register                    | No change                             |

| 4Bh  | Chip Select 0 Control Register                         | No change                             |

| 4Ch  | Chip Select 1 Base Address Register                    | No change                             |

| 4Dh  | Chip Select 1 Control Register                         | No change                             |

| 4Eh  | If AEh[7] = 0: Idle Reload Event<br>Enable Register 1  | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: Idle Reload Event<br>Enable Register 1A | New bits available "If AEh[7] = 1"    |

| 4Fh  | IDLE_TIMER Register                                    | No change                             |

| 50h  | PMU Control Register 3                                 | No change                             |

| 51h  | Beeper Control Register                                | No change                             |

| 52h  | Scratchpad Register 1                                  | No change                             |

| 53h  | Scratchpad Register 2                                  | No change                             |

| 54h  | Power Control Latch Register 1                         | No change                             |

| 55h  | Power Control Latch Register 2                         | No change                             |

| 56h  | Reserved                                               | No change                             |

| 57h  | PMU Control Register 4                                 | Bits [3,2], default changed           |

| 58h  | PMU Event Register 1                                   | No change                             |

| 59h  | PMU Event Register 2                                   | No change                             |

| Loc. | Register Name                                    | Revision                           |

|------|--------------------------------------------------|------------------------------------|

| 5Ah  | If AEh[7] = 0: PMU Event Register 3              | Added parameter "If<br>AEh[7] = 0" |

|      | If AEh[7] = 1: PMU Event Register 3A             | New bits available "If AEh[7] = 1" |

| 5Bh  | If AEh[7] = 0: PMU Event Register 4              | Added parameter "If<br>AEh[7] = 0" |

|      | If AEh[7] = 1: PMU Event Register 4A             | New bits available "If AEh[7] = 1" |

| 5Ch  | PMI SMI Source Register 1                        | No change                          |

| 5Dh  | If AEh[7] = 0: PMI SMI Source<br>Register 2      | No change                          |

|      | If AEh[7] = 1: PMI SMI Source<br>Register 2A     | Bit [3]                            |

| 5Eh  | Reserved                                         | No change                          |

| 5Fh  | PMU Control Register 5                           | No change                          |

| 60h  | R_Timer Count Register                           | No change                          |

| 61h  | Debounce Register                                | No change                          |

| 62h  | IRQ Doze Register 1                              | No change                          |

| 63h  | Idle Time-Out Select Register 1                  | No change                          |

| 64h  | INTRGRP IRQ Select Register 1                    | No change                          |

| 65h  | Doze Register                                    | No change                          |

| 66h  | PMU Control Register 6                           | Bits [3:1]                         |

| 67h  | PMU Control Register 7                           | No change                          |

| 68h  | Clock Source Register 2                          | No change                          |

| 69h  | R TIMER Register                                 | No change                          |

| 6Ah  | RSMGRP IRQ Register 1                            | No change                          |

| 6Bh  | Resume Source Register                           | Bits [6,5]                         |

| 6Ch  | Scratchpad Register 3                            | No change                          |

| 6Dh  | Scratchpad Register 4                            | No change                          |

| 6Eh  | Scratchpad Register 5                            | No change                          |

| 6Fh  | Scratchpad Register 6                            | No change                          |

| 70h  | GNR1 Base Address Register 1                     | No change                          |

| 71h  | GNR1 Control Register 1                          | No change                          |

| 72h  | GNR1 Control Register 2                          | No change                          |

| 73h  | GNR2 Base Address Register 1                     | No change                          |

| 74h  | GNR2 Control Register 1                          | No change                          |

| 75h  | GNR2 Control Register 2                          | No change                          |

| 76h  | If AEh[7] = 0: Doze Reload<br>Select Register 1  | Added parameter "If AEh[7] = 0"    |

|      | If AEh[7] = 1: Doze Reload<br>Select Register 1A | New bits available "If AEh[7] = 1" |

| 77h  | Doze Reload Select Register 2                    | No change                          |

| 78h  | Doze Reload Select Register 3                    | No change                          |

| 79h  | PMU Control Register 8                           | Bits [2,1]                         |

| 7Ah  | GNR3 Base Address Register 1                     | No change                          |

| 7Bh  | GNR3 Control Register 1                          | No change                          |

#### Table 5-5 SYSCFG 00h-FFh (cont.)

| Loc. | Register Name                               | Revision  |

|------|---------------------------------------------|-----------|

| 7Ch  | GNR3 Control Register 2                     | No change |

| 7Dh  | GNR4 Base Address Register 1                | No change |

| 7Eh  | GNR4 Control Register 1                     | No change |

| 7Fh  | GNR4 Control Register 2                     | No change |

| 80h  | ICW1 Shadow Register for INTC1              | No change |

| 81h  | ICW2 Shadow Register for INTC1              | No change |

| 82h  | ICW3 Shadow Register for INTC1              | No change |

| 83h  | ICW4 Shadow Register for INTC1              | No change |

| 84h  | DMA In-Progress Register                    | No change |

| 85h  | OCW2 Shadow Register for INTC1              | No change |

| 86h  | OCW3 Shadow Register for INTC1              | No change |

| 87h  | Reserved                                    | No change |

| 88h  | ICW1 Shadow Register for INTC2              | No change |

| 89h  | ICW2 Shadow Register for INTC2              | No change |

| 8Ah  | ICW3 Shadow Register for INTC2              | No change |

| 8Bh  | ICW4 Shadow Register for INCT2              | No change |

| 8Ch  | Reserved                                    | No change |

| 8Dh  | OCW2 Shadow Register for INTC2              | No change |

| 8Eh  | OCW3 Shadow Register for INTC2              | No change |

| 8Fh  | Reserved                                    | No change |

| 90h  | Timer Channel 0 Low Byte Register: A[7:0]   | No change |

| 91h  | Timer Channel 0 High Byte Register: A[15:8] | No change |

| 92h  | Timer Channel 1 Low Byte Register: A[7:0]   | No change |

| 93h  | Timer Channel 1 High Byte Register: A[15:8] | No change |

| 94h  | Timer Channel 2 Low Byte Register: A[7:0]   | No change |

| 95h  | Timer Channel 2 High Byte Register: A[15:8] | No change |

| 96h  | Write Counter High/Low Byte Latch           | No change |

| 97h  | Reserved                                    | No change |

| 98h  | RTC Index Shadow Register                   | No change |

| Loc.        | Register Name                                | Revision                           |

|-------------|----------------------------------------------|------------------------------------|

| 99h         | Interrupt Request Register for INCT1         | No change                          |

| 9Ah         | Interrupt Request Register for INCT2         | No change                          |

| 9Bh         | 3F2h + 3F7h Shadow Register                  | No change                          |

| 9Ch         | 372h + 377h Shadow Register                  | No change                          |

| 9Dh-<br>9Eh | Reserved                                     | No change                          |

| 9Fh         | Port 064h Shadow Register                    | No change                          |

| A0h         | Feature Control Register 1                   | No change                          |

| A1h         | Feature Control Register 2                   | No change                          |

| A2h         | If AEh[7] = 0: IRQ Doze Register 2           | Added parameter "If AEh[7] = 0"    |

|             | If AEh[7] = 1: IRQ Doze Register 2A          | New bits available "If AEh[7] = 1" |

| A3h         | Idle Time-Out Select Register 2              | No change                          |

| A4h         | INTRGRP IRQ Select Register 2                | No change                          |

| A5h         | Thermal Management Register 1                | No change                          |

| A6h         | Thermal Management Register 2                | No change                          |

| A7h         | Thermal Management Register 3                | No change                          |

| A8h         | Thermal Management Register 4                | No change                          |

| A9h         | Thermal Management Register 5                | No change                          |

| AAh         | Thermal Management Register 6                | No change                          |

| ABh         | Power Control Latch Register 3               | No change                          |

| ACh         | Reserved                                     | No change                          |

| ADh         | Feature Control Register 3                   | No change                          |

| AEh         | GNR_ACCESS Feature Register 1                | No change                          |

| AFh-<br>B0h | Reserved                                     | No change                          |

| B1h         | RSMGRP IRQ Register 2                        | No change                          |

| B2h         | If AEh[7] = 0: Clock Source Register 3       | Added parameter "If AEh[7] = 0"    |

|             | If AEh[7] = 1: Clock Source Register 3A      | New bits available "If AEh[7] = 1" |

| B3h         | Chip Select Cycle Type Register              | No change                          |

| B4h         | HDU_TIMER Register                           | No change                          |

| B5h         | COM1_TIMER Register                          | No change                          |

| B6h         | COM2_TIMER Register                          | No change                          |

| B7h         | If AEh[7] = 0: GNR2_TIMER<br>Register        | Added parameter "If AEh[7] = 0"    |

|             | If AEh[7] = 1: GNR6_TIMER<br>Register        | New bits available "If AEh[7] = 1" |

| B8h         | If AEh[7] = 0: GNR2 Base<br>Address Register | Added parameter "If<br>AEh[7] = 0" |

|             | If AEh[7] = 1: GNR6 Base<br>Address Register | New bits available "If AEh[7] = 1" |

## **Revision Document**

#### Table 5-5 SYSCFG 00h-FFh (cont.)

| Loc.        | Register Name                                                | Revision                                             |

|-------------|--------------------------------------------------------------|------------------------------------------------------|

| B9h         | If AEh[7] = 0: GNR2 Control<br>Register                      | Added parameter "If AEh[7] = 0"                      |

|             | If AEh[7] = 1: GNR6 Control<br>Register                      | New bits available "If AEh[7] = 1"                   |

| BAh         | Chip Select 2 Base Address Register                          | No change                                            |

| BBh         | Chip Select 2 Control Register                               | No change                                            |

| BCh         | Chip Select 3 Base Address Register                          | No change                                            |

| BDh         | Chip Select 3 Control Register                               | No change                                            |

| BEh         | If AEh[7] = 0: Idle Reload Event<br>Enable Register 2        | Added parameter "If<br>AEh[7] = 0"                   |

|             | If AEh[7] = 1: Idle Reload Event<br>Enable Register 2A       | New bits available "If<br>AEh[7] = 1"                |

| BFh         | Chip Select Granularity Register                             | No change                                            |

| C0h-<br>D4h | Reserved                                                     | No change                                            |

| D5h         | X Bus Positive Decode Register                               | Bits [7:0], new foot-<br>note                        |

| D6h         | PMU Control Register 9                                       | No change                                            |

| D7h         | Access Port Address Register 1                               | No change                                            |

| D8h         | If AEh[7] = 0: PMU Event Register 5                          | Added parameter "If<br>AEh[7] = 0" and bits<br>[7:0] |

|             | If AEh[7] = 1: PMU Event Register 5A                         | New bits available "If AEh[7] = 1"                   |

| D9h         | PMU Event Register 6                                         | No change                                            |

| DAh         | Power Management Event Status<br>Register                    | No change                                            |

| DBh         | If AEh[7] = 0: Next Access Event Generation Register 1       | Added parameter "If<br>AEh[7] = 0"                   |

|             | If AEh[7] = 1: Next Access Event Generation Register 1A      | New bits available "If AEh[7] = 1"                   |

| DCh         | If AEh[7] = 0: PMU SMI Source<br>Register 1                  | No change                                            |

|             | If AEh[7] = 1: PMU SMI Source<br>Register 1A                 | Bit 0                                                |

| DDh         | PMU SMI Source Register 2                                    | No changed                                           |

|             | FS ACPI                                                      | Bit 7                                                |

| DEh         | If AEh[7] = 0: Current Access<br>Event Generation Register 1 | Added parameter "If AEh[7] = 0"                      |

|             | If AEh[7] = 1: Current Access Event Generation Register 1A   | New bits available "If<br>AEh[7] = 1"                |

| DFh         | If AEh[7] = 0:Activity Tracking<br>Register 1                | Added parameter "If<br>AEh[7] = 0"                   |

|             | If AEh[7] = 1:Activity Tracking<br>Register 1A               | New bits available "If AEh[7] = 1"                   |

| Loc. | Register Name                                  | Revision                              |

|------|------------------------------------------------|---------------------------------------|

| E0h  | If AEh[7] = 0: Activity Tracking<br>Register 2 | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: Activity Tracking Register 2A   | New bits available "If AEh[7] = 1"    |

| E1h  | If AEh[7] = 0: GNR3 Base<br>Address Register   | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: GNR7 Base<br>Address Register   | New bits available "If<br>AEh[7] = 1" |

| E2h  | If AEh[7] = 0: GNR3 Control<br>Register        | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: GNR7 Control<br>Register        | New bits available "If AEh[7] = 1"    |

| E3h  | If AEh[7] = 0: GNR4 Base<br>Address Register   | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: GNR8 Base<br>Address Register   | New bits available "If AEh[7] = 1"    |

| E4h  | If AEh[7] = 0: GNR4 Control<br>Register        | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: GNR8 Control<br>Register        | New bits available "If AEh[7] = 1"    |

| E5h  | GNR_ACCESS Feature Register 2                  | Bit [6]                               |

| E6h  | If AEh[7] = 0: Clock Source Register 4         | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: Clock Source Register 4A        | New bits available "If AEh[7] = 1"    |

| E7h  | If AEh[7] = 0: GNR3_TIMER<br>Register          | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: GNR7_TIMER<br>Register          | New bits available "If AEh[7] = 1"    |

| E8h  | If AEh[7] = 0: GNR4_TIMER<br>Register          | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: GNR8_TIMER<br>Register          | New bits available "If AEh[7] = 1"    |

| E9h  | If AEh[7] = 0: PMU Event Register 7            | Added parameter "If AEh[7] = 0"       |

|      | If AEh[7] = 1: PMU Event Register 7A           | New bits available "If AEh[7] = 1"    |

| EAh  | If AEh[7] = 0: PMU SMI Source<br>Register 3    | No change                             |

|      | If AEh[7] = 1: PMU SMI Source<br>Register 3A   | Bits [1,0]                            |

| EBh  | Access Port Address Register 2                 | No change                             |

| ECh  | Write Trap Register 1                          | No change                             |

| EDh  | Write Trap Register 2                          | No change                             |

| EEh  | Power Control Latch Register 4                 | No change                             |

| EFh  | Hot Docking Control Register 1                 | No change                             |

| F0h  | Hot Docking Control Register 2                 | No change                             |

| F1h  | Low Order Start Address for ROM Window         | No change                             |

#### Table 5-5 SYSCFG 00h-FFh (cont.)

| Loc. | Register Name                           | Revision   |

|------|-----------------------------------------|------------|

| F2h  | High Order Start Address for ROM Window | No change  |

| F3h  | Thermal Management Register 7           | No change  |

| F4h  | Thermal Management Register 8           | No change  |

| F5h  | PMU Event Register 8                    | No change  |

|      | FS ACPI                                 | Bits [7,6] |

| F6h  | DMA Doze Reload Register 1              | No change  |

| F7h  | DMA Doze Reload Register 2              | No change  |

| F8h  | Compact ISA Control Register 1          | No change  |

| Loc. | Register Name                              | Revision       |

|------|--------------------------------------------|----------------|

| F9h  | Compact ISA Control Register 2             | No change      |

| FAh  | Compact ISA Control Register 3             | Bits [7,6]     |

| FBh  | DMA Idle Reload Register                   | No change      |

| FCh  | IDE Power Management Assignment Register 1 | Bits [7,6,3,2] |

| FDh  | IDE Power Management Assignment Register 2 | Bits [7,6,3,2] |

| FEh  | GPCS# Global Control Register              | No change      |

| FFh  | Reserved                                   | No change      |

#### 5.2 PCIDV0 Register Space

• Modified opening text slightly, removed reference to 82C701.

#### Table 5-6 PCIDV0 00h-FFh

| Loc.        | Register Name                              | Revision                                                    |

|-------------|--------------------------------------------|-------------------------------------------------------------|

| 00h         | Vendor Identification Register -<br>Byte 0 | No change                                                   |

| 01h         | Vendor Identification Register -<br>Byte 1 | No change                                                   |

| 02h         | Device Identification Register -<br>Byte 0 | No change                                                   |

| 03h         | Device Identification Register -<br>Byte 1 | No change                                                   |

| 04h         | Command Register - Byte 0                  | Changed reference<br>from 82C701 to<br>82C700 in bits [3:0] |

| 05h         | Command Register - Byte 1                  | No change                                                   |

| 06h         | Status Register - Byte 0                   | No change                                                   |

| 07h         | Status Register - Byte 1                   | Changed reference<br>from 82C701 to<br>82C700 in bits [3:2] |

| 08h         | Revision Identification Register           | Default changed                                             |

| 09h         | Class Code Register - Byte 0               | No change                                                   |

| 0Ah         | Class Code Register - Byte 1               | No change                                                   |

| 0Bh         | Class Code Register - Byte 2               | No change                                                   |

| 0Ch         | Reserved                                   | No change                                                   |

| 0Dh         | Master Latency Timer Register              | No change                                                   |

| 0Eh         | Header Type Register                       | No change                                                   |

| 0Fh         | Built-In Self-Test (BIST) Register         | No change                                                   |

| 10h-<br>2Bh | Reserved                                   | No change                                                   |

| Loc.        | Register Name                           | Revision                      |

|-------------|-----------------------------------------|-------------------------------|

| 2Ch-<br>2Dh | Subsystem Vendor ID                     | New register                  |

| 2Eh-<br>2Fh | Subsystem ID                            | New register                  |

| 30h-<br>3Fh | Reserved                                | No change                     |

| 40h         | Memory Control Register - Byte 0        | Bit [5]                       |

| 41h         | Memory Control Register - Byte 1        | No change                     |

| 42h         | Memory Control Register - Byte 2        | New register                  |

| 43h         | Internal Project Revision -<br>Reserved | New register                  |

| 44h         | Data Path Register 1                    | Bits [6:5]                    |

| 45h         | Data Path Control Register 2            | Bits [5,4,2,0]                |

| 46h         | Data Path Control Register 3            | No change                     |

| 47h         | Data Path Control Register 4            | Bits [6:3], new foot-<br>note |

| 48h         | Data Path Control Register 5            | New register                  |

| 49h-<br>4Bh | Reserved                                | No change                     |

| 4Ch         | MCACHE Control Register                 | New register                  |

| 4Dh         | Delay Adjustment Register               | New register                  |

| 4Eh         | SDRAM Control Register                  | New register                  |

| 4Fh-<br>FFh | Reserved                                | No change                     |

## **Revision Document**

#### 5.3 PCIDV1 Register Space

- Modified opening text slightly

- Added additional table (PCIDV1 table is now 5-8)

#### Table 5-8 PCIDV1 00h-FFh

| Loc.         | Register Name                              | Revision                 |  |

|--------------|--------------------------------------------|--------------------------|--|

| 00h          | Vendor Identification Register - Byte 0    | No change                |  |

| 01h          | Vendor Identification Register - Byte 1    | No change                |  |

| 02h          | Device Identification Register - Byte 0    | No change                |  |

| 03h          | Device Identification Register - Byte 1    | No change                |  |

| 04h          | Command Register - Byte 0                  | No change                |  |

| 05h          | Command Register - Byte 1                  | No change                |  |

| 06h          | Status Register - Byte 0                   | No change                |  |

| 07h          | Status Register - Byte 1                   | No change                |  |

| 08h          | Revision Identification Register           | Default changed          |  |

| 09h          | Class Code Register - Byte 0               | No change                |  |

| 0 <b>A</b> h | Class Code Register - Byte 1               | No change                |  |

| 0Bh          | Class Code Register - Byte 2               | No change                |  |

| 0Ch          | Reserved                                   | No change                |  |

| 0Dh          | Master Latency Timer Register              | No change                |  |

| 0Eh          | Header Type Register                       | No change                |  |

| 0Fh          | Built-In Self-Test (BIST) Register         | No change                |  |

| 10h-<br>2Bh  | Reserved                                   | No change                |  |

| 2Ch-<br>2Dh  | Subsystem Vendor ID                        | New register             |  |

| 2Eh-<br>2Fh  | Subsystem ID                               | New register             |  |

| 30h-<br>40h  | Reserved                                   | No change                |  |

| 41h          | Keyboard Controller Select Register        | Bit [3]                  |  |

| 42h          | Reserved                                   | No change                |  |

| 43h          | Feature Control Register                   | No change                |  |

| 44h-<br>45h  | Reserved                                   | No change                |  |

| 46h          | PCI Control Register B - Byte 0            | No change                |  |

| 47h          | PCI Control Register B - Byte 1            | No change                |  |

| 48h          | Strap Option Readback Register -<br>Byte 0 | No change                |  |

| 49h          | Strap Option Readback Register -<br>Byte 1 | Bits [4:0], new footnote |  |

| 4Ah          | ROM Chip Select Register 1                 | No change                |  |

| 4Bh          | ROM Chip Select Register 2                 | No change                |  |

| 4Ch-<br>4Dh  | Reserved                                   | No change                |  |

| 4Eh          | Miscellaneous Control Register 1           | Bits [7:4]               |  |

|              | FS ACPI                                    | Bits [5,4]               |  |

| Loc.        | Register Name                                                     | Revision       |

|-------------|-------------------------------------------------------------------|----------------|

| 4Fh         | Miscellaneous Control Register 2                                  | Bit [7,2], new |

|             | Ĭ                                                                 | footnote       |

|             | FS ACPI                                                           | Bit [7]        |

| 50h-<br>51h | Reserved                                                          | No change      |

| 52h         | Miscellaneous Controller Register 3                               | Bit [2]        |

|             | FS ACPI                                                           | Bits [4,3]     |

| 53h         | Miscellaneous Controller Register 4                               | Bits [7:1]     |

| 54h         | IRQ Driveback Address Register -<br>Byte 0: Address Bits [7:0]    | No change      |

| 55h         | IRQ Driveback Address Register -<br>Byte 1: Address Bits [15:8]   | No change      |

| 56h         | IRQ Driveback Address Register -<br>Byte 2: Address Bits [23:16]  | No change      |

| 57h         | IRQ Driveback Address Register -<br>Byte 3: Address Bits [31:24]  | No change      |

| 58h         | DRQ Remap Base Address Register -<br>Byte 0: Address Bits [7:0]   | No change      |

| 59h         | DRQ Remap Base Address Register -<br>Byte 1: Address Bits [15:8]  | No change      |

| 5Ah         | DRQ Remap Base Address Register -<br>Byte 2: Address Bits [23:16] | No change      |

| 5Bh         | DRQ Remap Base Address Register -<br>Byte 3: Address Bits [31:24] | No change      |

| 5Ch         | DMA Channel Selector Register                                     | No change      |

| 5Dh         | Reserved                                                          | No change      |

| 5Eh         | IRQ Scheme Management Register                                    | No change      |

| 5Fh         | SYSCFG Base Select Register                                       | No change      |

| 60h         | IRQ Driveback Data Register - Byte 0:<br>Data Bits [7:0]          | No change      |

| 61h         | IRQ Driveback Data Register - Byte 1:<br>Data Bits [15:8]         | No change      |

| 62h         | IRQ Driveback Data Register - Byte 2:<br>Data Bits [23:16]        | No change      |

| 63h         | IRQ Driveback Data Register - Byte 3:<br>Data Bits [31:24]        | No change      |

| 64h         | PCI Master Control Register 1                                     | No change      |

|             | FS ACPI                                                           | Bit [1]        |

| 65h         | PCI Master Control Register 2                                     | No change      |

|             | FS ACPI                                                           | Bit [6]        |

| 66h         | Reserved                                                          | No change      |

| 67h         | Miscellaneous Control Register 5                                  | Bits [1,0]     |

| 68h         | PCICLK Control Register 1                                         | No change      |

#### Table 5-8 PCIDV1 00h-FFh (cont.)

| Loc.        | Register Name                                  | Revision     |

|-------------|------------------------------------------------|--------------|

| 69h         | PCICLK Control Register 2                      | No change    |

| 6Ah         | PCICLK Skew Adjust Register for PCICLK 0, 1, 2 | No change    |

| 6Bh         | PCICLK Skew Adjust Register for PCICLK 3, 4, 5 | No change    |

| 6Ch-<br>6Fh | Reserved                                       | No change    |

| 70h         | Leakage Control Register - Byte 0              | Bits [1:0]   |

| 71h         | Leakage Control Register - Byte 1              | Bits [7:0]   |

| 72h         | Leakage Control Register - Byte 2              | Bits [7:4,1] |

| 73h         | Leakage Control Register - Byte 3              | Bits [5:4]   |

| 74h         | Leakage Control Register - Byte 4              | Bits [3:0]   |

| 75h         | Leakage Control Register - Byte 5              | Bits [7:2]   |

|             | FS ACPI                                        | Bits [3:2]   |

| 76h         | Hot Docking Leakage Control Register           | New register |

| 77h-<br>7Fh | Reserved                                       | No change    |

| 80h         | PIO0 Pin (CDOE#) Function Register             | No change    |

| 81h         | PIO1 Pin (TAGWE#) Function Register            | No change    |

| 82h         | PIO2 Pin (ADSC#) Function Register             | No change    |

| 83h         | PIO3 Pin (ADV#) Function Register              | No change    |

| 84h         | PIO4 Pin (RAS2#) Function Register             | No change    |

| 85h         | PIO5 Pin (RAS1#) Function Register             | No change    |

| 86h         | PIO6 Pin (CLKRUN#) Function Register           | No change    |

| 87h         | PIO7 Pin (REQ1#) Function Register             | No change    |

| 88h         | PIO8 Pin (REQ2#) Function Register             | No change    |

| 89h         | PIO9 Pin (DDRQ0) Function Register             | No change    |

| 8Ah         | PIO10 Pin (IRQ1) Function Register             | No change    |

| 8Bh         | PIO11 Pin (IRQ8#) Function Register            | No change    |

| 8Ch         | PIO12 Pin (IRQ12) Function Register            | No change    |

| 8Dh         | PIO13 Pin (IRQ14) Function Register            | No change    |

| 8Eh         | PIO14 Pin (SEL#/ATB#) Function<br>Register     | No change    |

| 8Fh         | PIO15 Pin (RSTDRV) Function Register           | No change    |

| 90h         | PIO16 Pin (SA16) Function Register             | No change    |

| 91h         | PIO17 Pin (SA17) Function Register             | No change    |

| 92h         | PIO18 Pin (IO16#) Function Register            | No change    |

| 93h         | PIO19 Pin (M16#) Function Register             | No change    |

| 94h         | PIO20 Pin (SBHE#) Function Register            | No change    |

| 95h         | PIO21 Pin (SMRD#) Function Register            | No change    |

| 96h         | PIO22 Pin (SMWR#) Function Register            | No change    |

| 97h         | PIO23 Pin (ROMCS#) Function Register           | No change    |

| Loc.        | Register Name                              | Revision  |

|-------------|--------------------------------------------|-----------|

| 98h         | PIO24 Pin (KBDCS#) Function Register       | No change |

| 99h         | PIO25 Pin (DRQA) Function Register         | No change |

| 9Ah         | PIO26 Pin (DRQB) Function Register         | No change |

| 9Bh         | PIO27 Pin (DRQC) Function Register         | No change |

| 9Ch         | PIO28 Pin (DRQD) Function Register         | No change |

| 9Dh         | PIO29 Pin (DRQE) Function Register         | No change |

| 9Eh         | PIO30 Pin (DRQF) Function Register         | No change |

| 9Fh         | PIO31 Pin (DRQG) Function Register         | No change |

| A0h         | Logic Matrix Register 1                    | No change |

| A1h         | Logic Matrix Register 2                    | No change |

| A2h         | Logic Matrix Register 3                    | No change |

| A3h         | Logic Matrix Register 4                    | No change |

| A4h         | Logic Matrix Register 5                    | No change |

| A5h         | Logic Matrix Register 6                    | No change |

| A6h         | Logic Matrix Register 7                    | No change |

| A7h         | Logic Matrix Register 8                    | No change |

| A8h         | PIO Pin Current State Register 1           | No change |

| A9h         | PIO Pin Current State Register 2           | No change |

| AAh         |                                            |           |

| ABh         | PIO Pin Current State Register 4           | No change |

| ACh-<br>ADh | Reserved                                   | No change |

| AEh         | DBE# Select Register 1                     | No change |

| AFh         | DBE# Select Register 2                     | No change |

| B0h         | IRQA Interrupt Selection Register          | No change |

| B1h         | IRQB Interrupt Selection Register          | No change |

| B2h         | IRQC Interrupt Selection Register          | No change |

| B3h         | IRQD Interrupt Selection Register          | No change |

| B4h         | IRQE Interrupt Selection Register          | No change |

| B5h         | IRQF Interrupt Selection Register          | No change |

| B6h         | IRQG Interrupt Selection Register          | No change |

| B7h         | IRQH Interrupt Selection Register          | No change |

| B8h         | PCI Interrupt Selection Register 1         | No change |

| B9h         | PCI Interrupt Selection Register 2         | No change |

| BAh         | Serial IRQ Control Register 1              | No change |

| BBh         | Serial IRQ Control Register 2              | No change |

| BCh-<br>BFh | Reserved                                   | No change |

| C0h         | DMA Channels A and B Selection<br>Register | No change |

| C1h         | DMA Channels C and D Selection<br>Register | No change |

| C2h         | DMA Channel E Selection Register           | No change |

| C3h         | DMA Channels F and G Selection<br>Register | No change |

## **Revision Document**

#### Table 5-8 PCIDV1 00h-FFh (cont.)

| Loc.                                                                         | Register Name                                                           | Revision     |  |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------|--|

| C4h-<br>CFh                                                                  | Reserved No change                                                      |              |  |

| Note:                                                                        | PCIDV1 D0h through EEh pertain oversion. Otherwise they are reserv      | •            |  |

| D0h                                                                          | FS ACPI: PM1_BLK Base Address<br>Register - Byte 0: Address Bits [7:0]  | New register |  |

| D1h                                                                          | FS ACPI: PM1_BLK Base Address<br>Register - Byte 1: Address Bits [15:8] | New register |  |

| D2h                                                                          | FS ACPI: PM2_BLK Base Address<br>Register - Byte 0: Address Bits [7:0]  | New register |  |

| D3h                                                                          | FS ACPI: PM2_BLK Base Address<br>Register -Byte 1: Address Bits [15:8]  | New register |  |

| D4h                                                                          | FS ACPI: P_BLK Base Address Register - Byte 0: Address Bits [7:0]       | New register |  |

| D5h                                                                          | FS ACPI: P_BLK Base Address Register - Byte 1: Address Bits [15:8]      | New register |  |

| D6h                                                                          | FS ACPI: GPE0_BLK Base Address<br>Register - Byte 0: Address Bits [7:0] | New register |  |

| D7h FS ACPI: GPE0_BLK Base Address<br>Register - Byte 0: Address Bits [15:8] |                                                                         | New register |  |

| D8h                                                                          | FS ACPI: ACPI Source Control Register - Byte 0                          | New register |  |

| D9h                                                                          | FS ACPI: ACPI Source Control Register - Byte 1                          | New register |  |

| DAh                                                                          | FS ACPI: ACPI Source Status Register - Byte 0                           | New register |  |

| DBh                                                                          | FS ACPI: ACPI Source Status Register - Byte 1                           | New register |  |

| DCh                                                                          | FS ACPI: ACPI Event Resume Control<br>Register - Byte 0                 | New register |  |

| DDh FS ACPI: ACPI Event Resume C<br>Register - Byte 1                        |                                                                         | New register |  |

| DEh-<br>DFh                                                                  | Reserved                                                                | New register |  |

| Loc.        | Register Name                                        | Revision     |

|-------------|------------------------------------------------------|--------------|

| E0h         | FS ACPI: SLP_TYP Control Register -<br>Byte 0        | New register |

| E1h         | FS ACPI: SLP_TYP Control Register -<br>Byte 1        | New register |

| E2h         | FS ACPI: SLP_TYP Control Register -<br>Byte 2        | New register |

| E3h         | FS ACPI: SLP_TYP Control Register -<br>Byte 3        | New register |

| E4h         | FS ACPI: SLP_TYP Control Register -<br>Byte 4        | New register |

| E5h         | FS ACPI: SLP_TYP Control Register -<br>Byte 5        | New register |

| E6h         | FS ACPI: SLP_TYP Control Register -<br>Byte 6        | New register |

| E7h         | FS ACPI: SLP_TYP Control Register -<br>Byte 7        | New register |

| E8h         | FS ACPI: Power Control Latch Set<br>Register         | New register |

| E9h         | Reserved                                             | New register |

| EAh         | FS ACPI: Power Control Readback<br>Register - Byte 0 | New register |

| EBh         | FS ACPI: Power Control Readback<br>Register - Byte 1 | New register |

| ECh         | FS ACPI: Power Control Readback<br>Register - Byte 2 | New register |

| EDh         | FS ACPI: Power Control Readback<br>Register - Byte 3 | New register |

| EEh         | FS ACPI: ACPI Thermal Control Register               | New register |

| EFh-<br>FDh | Reserved                                             | No change    |

| FEh         | Stop Grant Cycle Generation Register                 | No change    |

| FFh         | Parity Error Cycle Generation Register               | No change    |

#### 5.4 IDE Register Space

#### 5.4.1 IDE Configuration Registers

• No change in opening text

#### Table 5-9 PCIIDE 00h-47h

| Loc                                                                | Register Name                                                    | Revision          |  |

|--------------------------------------------------------------------|------------------------------------------------------------------|-------------------|--|

| 00h                                                                | Vendor ID Register - Byte 0                                      | No change         |  |

| 01h                                                                | Vendor ID Register - Byte 1 No change                            |                   |  |

| 02h                                                                |                                                                  |                   |  |

| 03h                                                                | Device ID Register - Byte 1                                      | No change         |  |

| 04h                                                                | Command Register - Byte 0                                        | No change         |  |

| 05h                                                                | Command Register - Byte 1                                        | No change         |  |

| 06h                                                                | Status Register - Byte 0                                         | No change         |  |

| 07h                                                                | Status Register - Byte 1                                         | No change         |  |

| 08h                                                                | Revision ID Register                                             | No change         |  |

| 09h                                                                | Class Code Register - Byte 0                                     | No change         |  |

| 0Ah                                                                | Class Code Register - Byte 1                                     | No change         |  |

| 0Bh                                                                | Class Code Register - Byte 2                                     | No change         |  |

| 0Ch-<br>0Dh                                                        | Reserved                                                         | No change         |  |

| 0Eh                                                                | Header Type Register                                             | No change         |  |

| 0Fh                                                                | Built-In Self-Test Register                                      | No change         |  |

| 10h- Primary IDE Command Block Base Clarified 13h Address Register |                                                                  | Clarified default |  |

| 14h-<br>17h                                                        | Primary IDE Control Block Base<br>Address Register               | Clarified default |  |

| 18h-<br>1Bh                                                        | Secondary IDE Command Block Base Address Register  Clarified def |                   |  |

| 1Ch-<br>1Fh                                                        | Secondary IDE Control Block Base<br>Address Register             | Clarified default |  |

| 20h-<br>23h                                                        | Bus Master IDE Base Address<br>Register                          | Default changed   |  |

| 24h-<br>2Bh                                                        | Reserved                                                         | No change         |  |

| 2Ch-<br>2Dh                                                        | Subsystem Vendor ID                                              | New register      |  |

| 2Eh-<br>2Fh                                                        | Subsystem ID                                                     | New register      |  |

| 30h-<br>3Ah                                                        | Reserved                                                         | No change         |  |

| 3Ch                                                                | Interrupt Line Register                                          | Default changed   |  |

| 3Dh                                                                | Interrupt Pin Register                                           | No change         |  |

| 3Eh-<br>3Fh                                                        | Reserved                                                         | No change         |  |

| 40h                                                                | IDE Initialization Control Register                              | No change         |  |

| 41h                                                                | Reserved                                                         | No change         |  |

| Loc     | Register Name                                  | Revision      |  |

|---------|------------------------------------------------|---------------|--|

| 42h     | IDE Enhanced Feature Register                  | No change     |  |

|         | FS ACPI: IDE Enhanced Feature<br>Register      | Bit [6]       |  |

| 43h     | IDE Enhanced Mode Register                     | No change     |  |

|         |                                                |               |  |

| Note: T | ne registers differ for FireStar and FS A      | CPI from 44h. |  |

| FireSta | •                                              |               |  |

| 44h     | Emulated Bus Master Register                   | No change     |  |

| 45h     | IDE Interrupt Selection Register               | No change     |  |

| FireSta | ACPI                                           |               |  |

| 44h     | FS ACPI: Ultra DMA Configuration<br>Register 1 | New register  |  |

| 45h     | FS ACPI: Ultra DMA Configuration Register 2    | New register  |  |

| 46h     | FS ACPI: Emulated IDE Configuration Register   | New location  |  |

| 47h     | FS ACPI: IDE Interrupt Selection Register      | New location  |  |

#### 5.4.2 IDE I/O Registers

No changes

#### 5.5 I/O Registers

- Changed title of Table 5-13

- Added ACPI I/O registers

#### 5.6 Register Space Summary

Updated with changes made to SYSCFG and PCICFG registers

### **Revision Document**

#### Section 6.0 Electrical Ratings

· Changed section title

#### 6.1 Absolute Maximum Ratings

· No changes

#### 6.2 DC Characteristics

· Modified table, now have one DC table as opposed to four

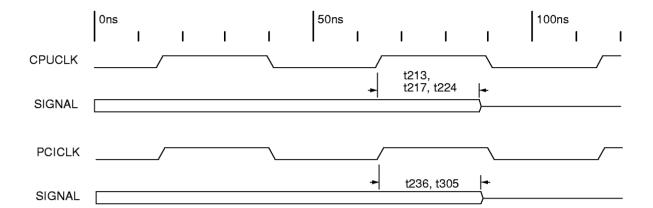

#### 6.3-6.7 AC Characteristics

No changes made to the AC characteristic for the individual modules

#### 6.8 AC Timing Diagrams

· No changes

#### **Section 7.0 Test Mode Information**

New section to data book

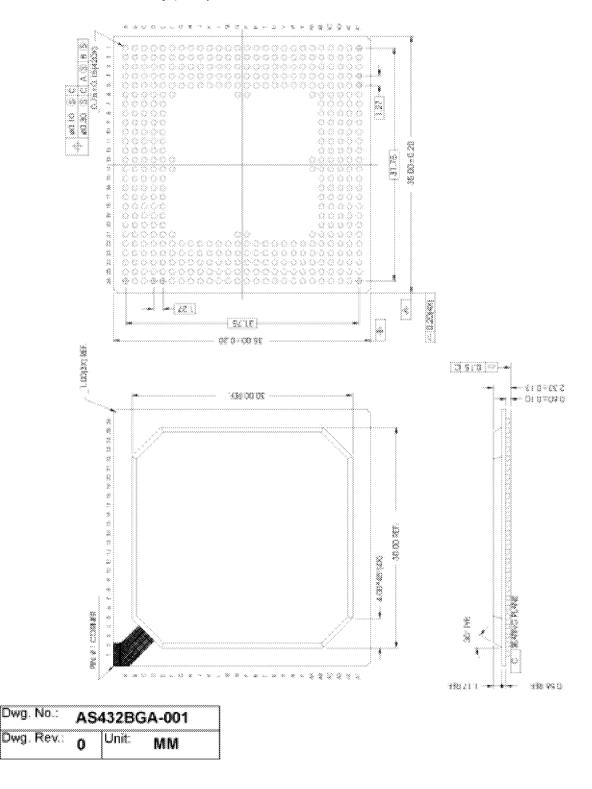

### Section 8.0 Mechanical Package Outline

No changes

## **Table of Contents**

| 1.0 | Features   |                    |                                                              |            |  |

|-----|------------|--------------------|--------------------------------------------------------------|------------|--|

| 2.0 | 0 Overview |                    |                                                              |            |  |

| 3.0 | Sigi       | Signal Definitions |                                                              |            |  |

|     | 3.1        | Termir             | nology/Nomenclature Conventions                              | 4          |  |

|     | 3.2        |                    | Descriptions                                                 |            |  |

|     |            | 3.2.1              | CPU Interface Signals Set                                    |            |  |

|     |            | 3.2.2              | DRAM and PCI Interface Signals Set                           | 15         |  |

|     |            | 3.2.3              | IDE Interface Signal Set                                     | 19         |  |

|     |            | 3.2.4              | ISA Interface Signal Set                                     | 21         |  |

|     |            | 3.2.5              | Test Mode Selection Pins                                     | 32         |  |

|     |            | 3.2.6              | Power and Ground Pins                                        | 32         |  |

|     | 3.3        | Progra             | ammable I/O Pins                                             | 33         |  |

|     | 3.4        | Strap              | Selected Options                                             | 39         |  |

| 4.0 | Fun        | ctional            | I Description                                                | 41         |  |

|     | 4.1        | Buses              | and Concurrency                                              | 41         |  |

|     |            | 4.1.1              | Cycles Originating from CPU                                  | 41         |  |

|     |            |                    | 4.1.1.3 Cycles Destined for a Docking Station ISA Bus Device |            |  |

|     |            | 4.1.2              | Concurrent Bus Operation                                     | 43         |  |

|     | 4.2        | Interm             | odule Communications                                         | 43         |  |

|     |            | 4.2.1              | Read: CPU < DRAM or L2 Cache                                 | 43         |  |

|     |            | 4.2.2              | Write: CPU > DRAM or L2 Cache                                | 43         |  |

|     |            | 4.2.3              | Cache Write Hit - Write Cycles from CPU to L2 Cache          |            |  |

|     |            | 4.2.4              | L2 Cache Inquiries from PCI                                  |            |  |

|     | 4.3        | Reset              | Logic                                                        | <b>4</b> 4 |  |

| 4.4 | System Clocks |                                                                   |    |

|-----|---------------|-------------------------------------------------------------------|----|

|     | 4.4.1         | CPU and FireStar Clocks                                           | 45 |

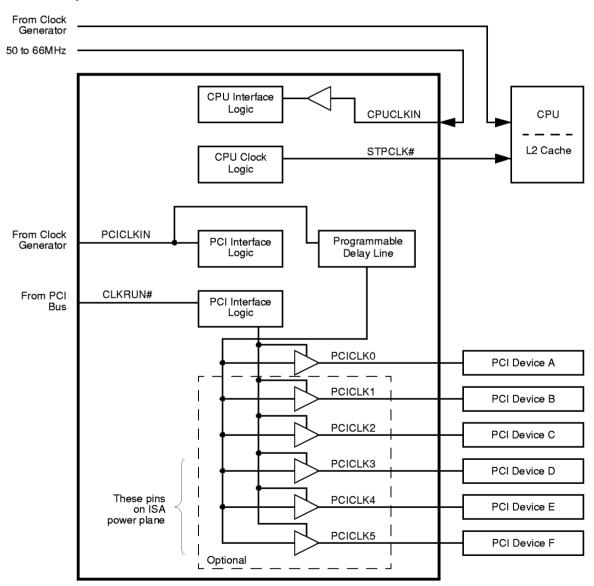

|     | 4.4.2         | PCI Bus Clocks                                                    | 45 |

|     |               | 4.4.2.1 PCI Clock Generation                                      |    |

|     | 4.4.3         | ISA Bus Clocks                                                    | 48 |

|     | 4.4.4         | Clock Control                                                     | 48 |

|     | 4.4.5         | L2 Cache Clock Control                                            | 48 |

| 4.5 | Cache         | Cache Subsystem                                                   |    |

|     | 4.5.1         | CPU Burst Mode Control                                            | 49 |

|     |               | 4.5.1.1 Cyrix Linear Burst Mode Support                           | 49 |

|     | 4.5.2         | Cache Cycle Types                                                 | 50 |

|     | 4.5.3         | Cache Operation                                                   | 50 |

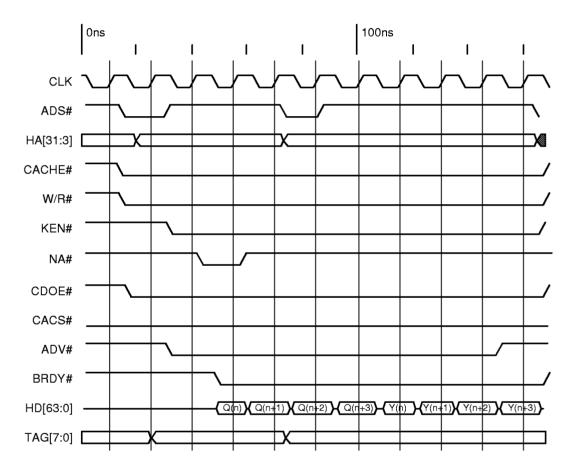

|     |               | 4.5.3.1 L2 Cache Read Hit                                         | 50 |

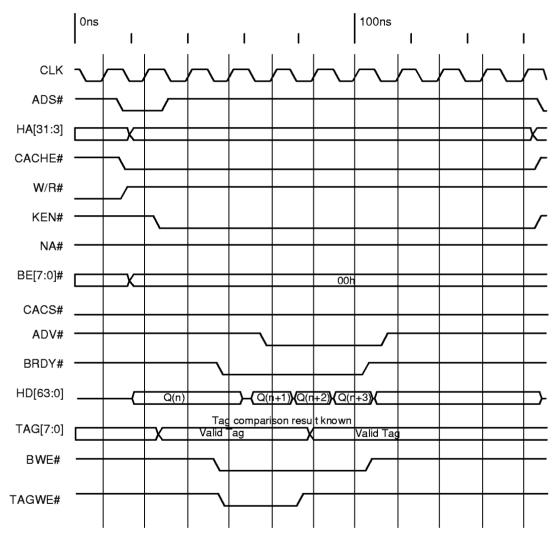

|     |               | 4.5.3.2 L2 Cache Write Hit Cycle                                  | 52 |

|     |               | 4.5.3.3 L2 Cache Read Miss                                        | 53 |

|     |               | 4.5.3.4 L2 Cache Write Miss                                       | 53 |

|     |               | 4.5.3.5 Write Policies                                            | 53 |

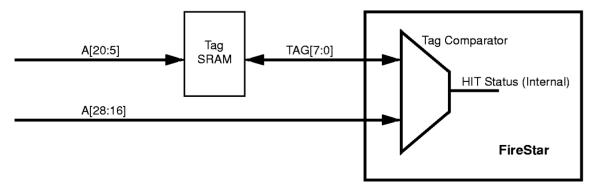

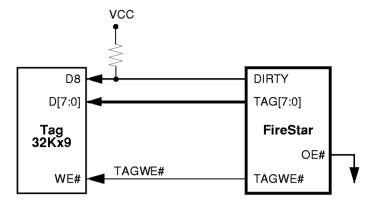

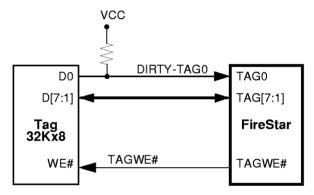

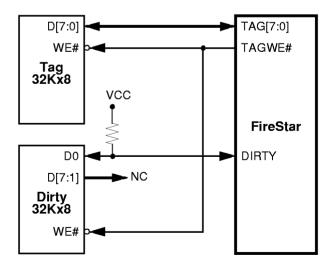

|     |               | 4.5.3.6 Tag Compare Table                                         | 55 |

|     |               | 4.5.3.7 Tag and Dirty RAM Implementations                         | 56 |

|     |               | 4.5.3.8 Cache Initialization                                      | 58 |

|     |               | 4.5.3.9 Write Back Cache with DMA/ISA Master/PCI Master Operation | 58 |

|     | 4.5.4         | Shadow ROM and BIOS Cacheability                                  | 62 |

|     |               | 4.5.4.1 Cacheability and Write Protection                         | 63 |

|     |               | 4.5.4.2 Remapping of Reset Vector to Shadow DRAM                  | 66 |

|     | 4.5.5         | SRAM Support                                                      | 67 |

|     |               | 4.5.5.1 SRAM Requirements                                         | 67 |

|     |               | 4.5.5.2 Pipelined Synchronous SRAM Support                        | 67 |

|     |               | 4.5.5.3 Sony SONIC-2WP (Cache Module) Support                     | 70 |

| 4.6 | DRAM          | l Controller                                                      | 71 |

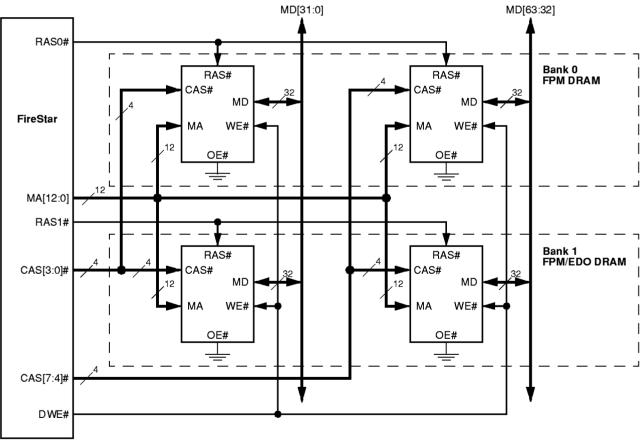

|     | 4.6.1         | FPM and EDO DRAM Support                                          | 71 |

|     |               | 4.6.1.1 DRAM Type Detection Algorithm                             | 72 |

|     | 4.6.2         | EDO Support                                                       | 74 |

|     | 4.6.3         | SDRAM Support                                                     | 76 |

|     |               | 4.6.3.1 SDRAM Commands                                            | 76 |

|     |               | 4.6.3.2 SDRAM Initialization                                      | 76 |

|     |                        | 4.6.3.3            | Unbuffered DIMMs                      |     |

|-----|------------------------|--------------------|---------------------------------------|-----|

|     |                        | 4.6.3.4            | SDRAM Detection Algorithm             |     |

|     | 4.6.4                  |                    | Buffering                             |     |

|     |                        | 4.6.4.1            | CPU-to-DRAM Deep Buffer               |     |

|     |                        | 4.6.4.2            | PCI-to-DRAM Deep Buffer               |     |

|     | 4.6.5                  | J                  | nming the DRAM Parameters             |     |

|     |                        | 4.6.5.1            | Drive Strengths                       |     |

|     |                        | 4.6.5.2<br>4.6.5.3 | Number of DRAM banks DRAM Size        |     |

|     |                        |                    |                                       |     |

|     | 4.6.6                  |                    | Cycles                                |     |

|     |                        | 4.6.6.1            | DRAM Write Cycle                      |     |

|     |                        | 4.6.6.2<br>4.6.6.3 | DRAM Write Cycle DRAM Refresh Logic   |     |

|     | 407                    |                    | <b>y</b>                              |     |

|     | 4.6.7                  |                    | DMA/Master Cycles                     |     |

|     | 4.6.8                  | DRAM H             | Hole Control                          | 93  |

| 4.7 | CPU Pipelining Control |                    |                                       | 94  |

| 4.8 | PCI Bu                 | s Interfac         | ce                                    | 97  |

|     | 4.8.1                  | PCI Mas            | ster Cycles                           | 97  |

|     |                        | 4.8.1.1            | System Memory Access                  | 97  |